# HC89S003F4 Datasheet

# 20Pin 8bit FLASH Microcontroller with ADC Peripheral function Ports total mapping

# **Contents**

1 DESCRIPTION......5

| 1.1  | Features                                           | 5  |

|------|----------------------------------------------------|----|

| 1.2  | SYSTEM DIAGRAM                                     | 6  |

| 1.3  | PIN CONFIGURATION                                  | 7  |

| 1.4  | PIN DESCRIPTION                                    | 7  |

| 1.5  | PERIPHERAL FUNCTION PORTS TOTAL MAPPING MODULE PTM | 8  |

| 2 C  | PU                                                 | 10 |

| 2.1  | CPU CHARACTERISTICS                                | 10 |

| 2.2  | CPU registers                                      | 10 |

| 3 M  | IEMORY                                             | 12 |

| 3.1  | THE PROGRAM MEMORY(FLASH)                          | 12 |

| 3.2  | Data storage (RAM)                                 |    |

| 3.3  | SPECIAL FUNCTION REGISTERS (SFR)                   | 19 |

| 4 TI | HE SYSTEM CLOCK                                    | 22 |

| 4.1  | CHARACTERISTICS OF THE SYSTEM CLOCK                | 22 |

| 4.2  | SYSTEM CLOCK REGISTERS                             |    |

| 5 P( | OWER MANAGEMENT                                    | 26 |

| 5.1  | POWER MANAGEMENT CHARACTERISTICS                   |    |

| 5.2  | IDLE MODE                                          |    |

| 5.3  | POWER-DOWN MODE                                    |    |

| 5.4  | POWER MANAGEMENT REGISTERS                         |    |

| 6 R  | ESET                                               | 28 |

| 6.1  | RESET CHARACTERISTICS                              | 28 |

| 6.2  | POR ( POWER-ON RESET )                             |    |

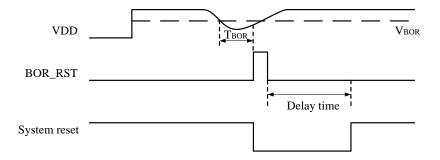

| 6.3  | BOR (Brown-out reset)                              |    |

| 6.4  | External reset                                     | 28 |

| 6.5  | EXTERNAL PORT LOW-VOLTAGE DETECTION RESET          | 28 |

| 6.6  | SOFTWARE RESET                                     | 29 |

| 6.7  | WATCHDOG (WDT) RESET                               | 29 |

| 6.8  | STACK OVERFLOW RESET                               | 29 |

| 6.9  | RESET REGISTERS                                    | 29 |

| 7 G  | ENERAL AND MULTIPLEXED I/O                         | 32 |

| 7.1  | GENERAL AND MULTIPLEXED I/O CHARACTERISTICS        | 32 |

| 7.2  | I/O MODE                                           | 32 |

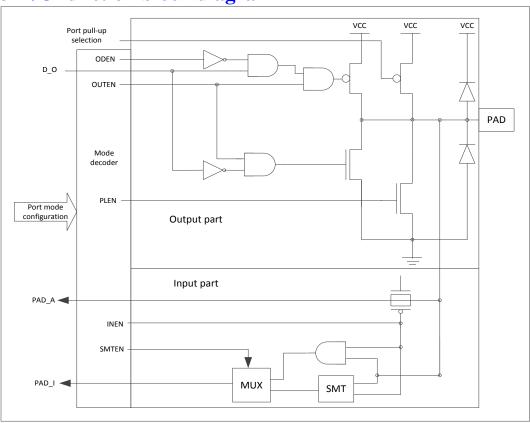

| 7.3  | I/O FUNCTION BLOCK DIAGRAM                         | 32 |

| 7.4  | I/O PORT REGISTERS                                 | 32 |

| 7.5  | PERIPHERAL FUNCTION PORTS TOTAL MAPPING CONTROL    | 36 |

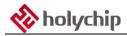

| 8 IN | NTERRUPT                                           | 39 |

| 8.1  | Interrupt characteristics                          | 39 |

| 8.2  | Interrupt summary                                  | 39 |

| 8.3  | INTERRUPT VECTORS                                  | 40 |

| 8.4  | INTERRUPT PRIORITIES                               | 40 |

| 8.5    | INTERRUPT HANDLING                     | 40 |

|--------|----------------------------------------|----|

| 8.6    | External interrupt                     | 41 |

| 8.7    | INTERRUPT REGISTERS                    | 41 |

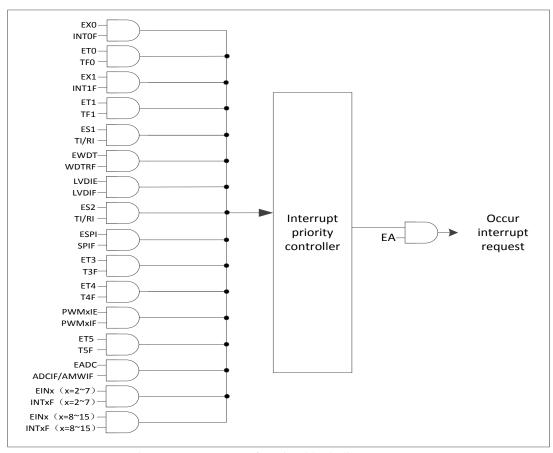

| 9 TIN  | MER/COUNTER                            | 46 |

| 9.1    | TIMER/COUNTER CHARACTERISTICS          | 46 |

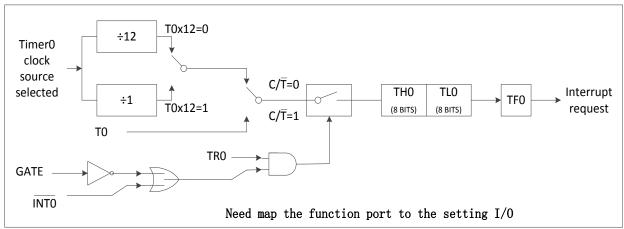

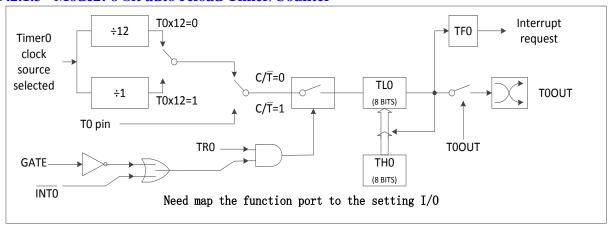

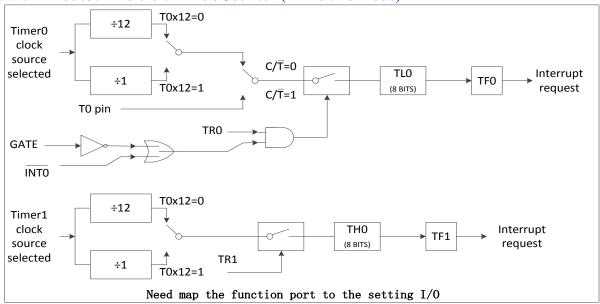

| 9.2    | TIMER/COUNTER $Tx(x = 0,1)$            | 46 |

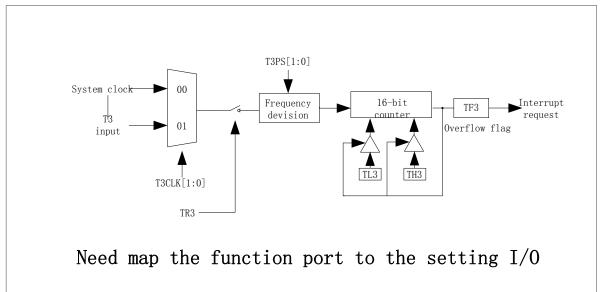

| 9.3    | TIMER 3                                | 50 |

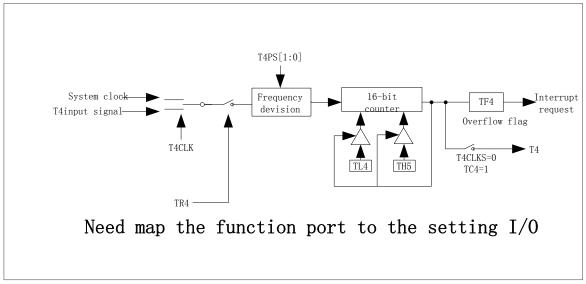

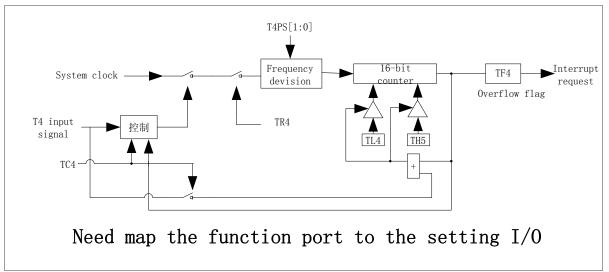

| 9.4    | TIMER/COUNTER 4                        | 52 |

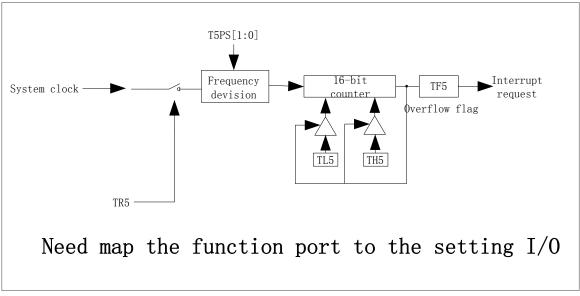

| 9.5    | TIMER 5                                | 56 |

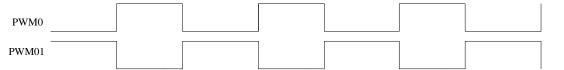

| 10 PU  | LSE WIDTH MODULATION PWM               | 60 |

| 10.1   | PWM CHARACTERISTICS                    | 60 |

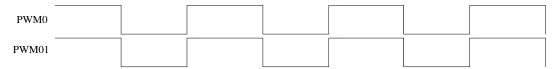

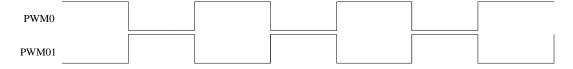

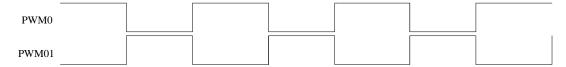

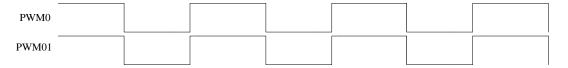

| 10.2   | PWM OUTPUT MODE                        | 60 |

| 10.3   | PWM REGISTERS                          | 61 |

| 11 SIN | NGLE 8 BIT PWM                         | 72 |

| 11.1   | PWM CHARACTERISTICS                    | 72 |

| 11.2   | PWM MODULE REGISTERS                   | 72 |

| 12 WA  | ATCHDOG TIMER WDT                      | 74 |

| 12.1   | WDT CHARACTERISTICS                    | 74 |

| 12.2   | WDT registers                          | 74 |

| 13 UN  | IIVERSAL ASYNCHRONOUS TRANSCEIVER UART | 76 |

| 13.1   | UART CHARACTERISTICS                   | 76 |

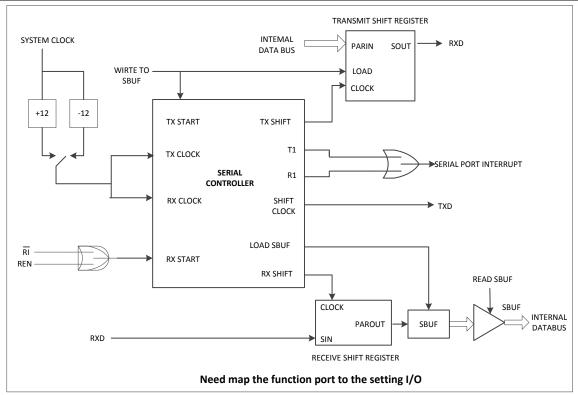

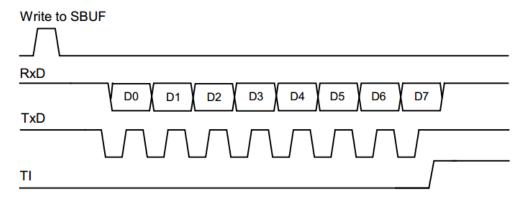

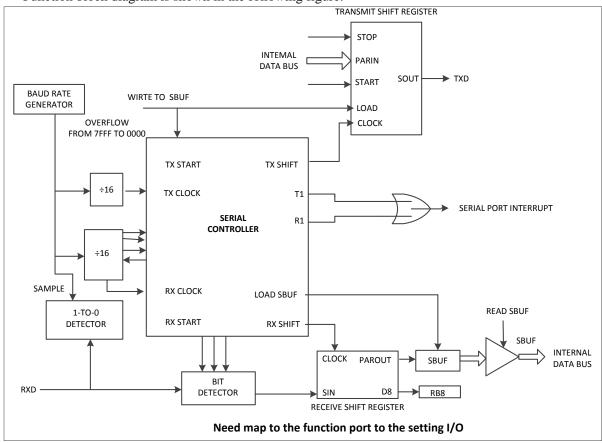

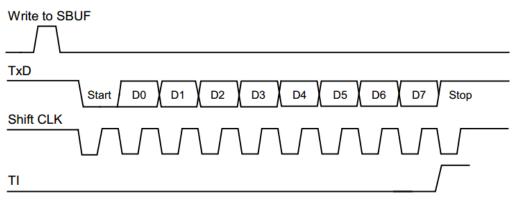

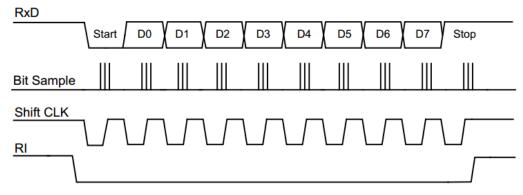

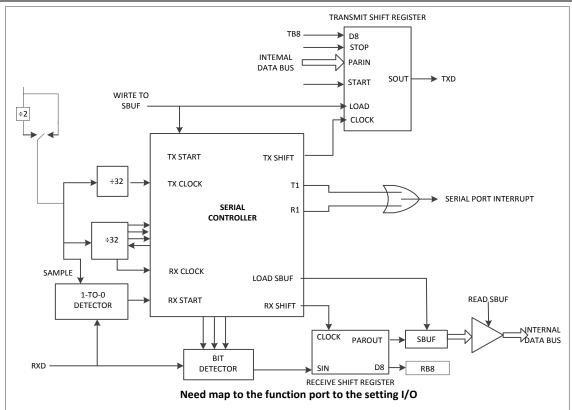

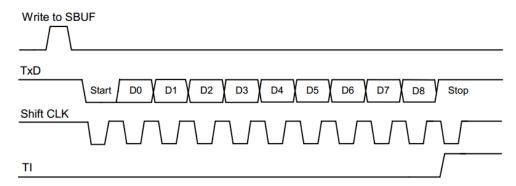

| 13.2   | Work mode                              | 76 |

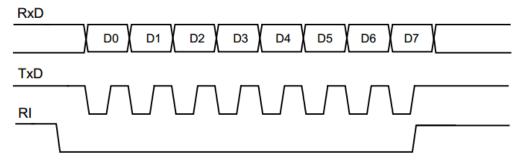

| 13.3   | BAUD RATE GENERATOR                    | 82 |

| 13.4   | MULTIPROCESSOR COMMUNICATION           | 82 |

| 13.5   | FRAME ERROR DETECTION                  | 83 |

| 13.6   | UART1 REGISTERS                        | 84 |

| 13.7   | UART2                                  | 86 |

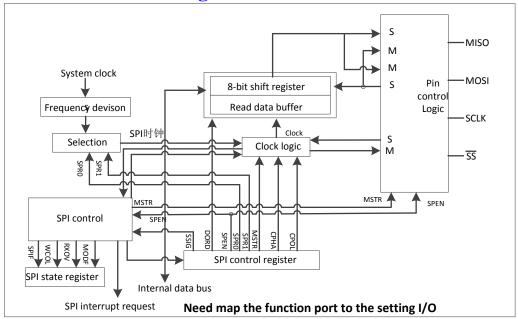

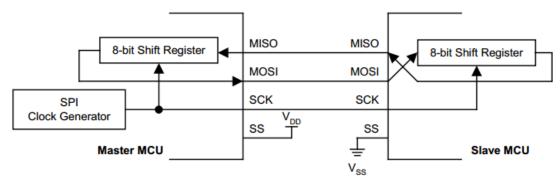

| 14 SEI | RIAL PERIPHERAL INTERFACE SPI          | 90 |

| 14.1   | SPI CHARACTERISTICS                    | 90 |

| 14.2   | SPI SIGNAL DESCRIPTION.                | 90 |

| 14.3   | SPI CLOCK RATE                         | 90 |

| 14.4   | SPI FUNCTIONAL BLOCK DIAGRAM           | 91 |

| 14.5   | SPI WORK MODE                          | 91 |

| 14.6   | SPI TRANSFER FORM                      |    |

| 14.7   | SPI Error detection                    | 93 |

| 14.8   | SPI INTERRUPT                          |    |

| 14.9   | SPI CONFIGURATION TABLE                |    |

| 14.10  | SPI REGISTERS                          | 95 |

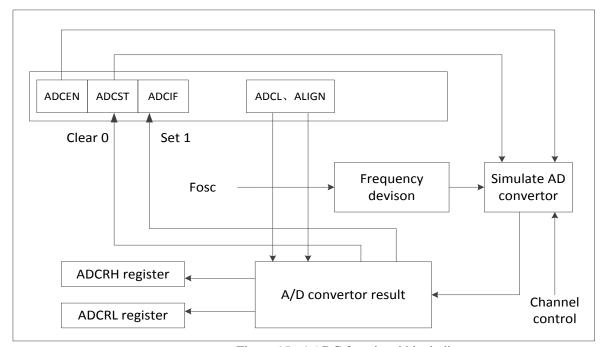

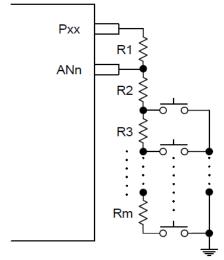

| 15 AN  | ALOG TO DIGITAL CONVERTER ADC          | 97 |

| 15.1   | ADC CHARACTERISTICS                    | 97 |

| 15.2   | ADC POWER SAVING WAKEUP                | 97 |

| 15.3 | ADC registers                                | 98  |

|------|----------------------------------------------|-----|

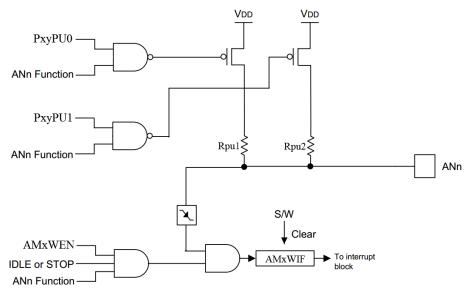

| 16 L | OW VOLTAGE DETECTION LVD                     | 102 |

| 16.1 | LVD CHARACTERISTICS                          | 102 |

| 16.2 | 2 LVD registers                              | 102 |

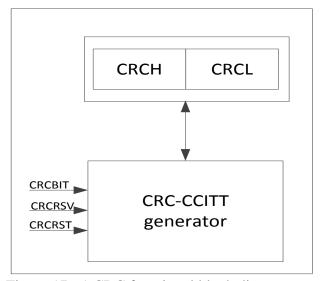

| 17 C | CYCLIC REDUNDANCY CHECK CRC                  | 104 |

| 17.1 | CRC CHARACTERISTICS                          | 104 |

| 17.2 | 2 CRC registers                              | 104 |

| 18 C | CODE OPTIONS                                 | 106 |

| 19 E | LECTRICAL CHARACTERISTICS                    | 107 |

| 19.1 | LIMIT PARAMETER                              | 107 |

| 19.2 | 2 DC CHARACTERISTICS                         | 107 |

| 19.3 | AC CHARACTERISTICS                           | 109 |

| 19.4 | ADC CHARACTERISTICS                          | 109 |

| 19.5 | BOR DETECTION VOLTAGE CHARACTERISTICS        | 110 |

| 19.6 | 5 LVD/PLVD DETECTION VOLTAGE CHARACTERISTICS | 110 |

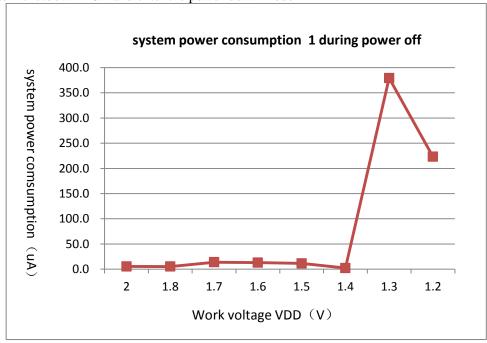

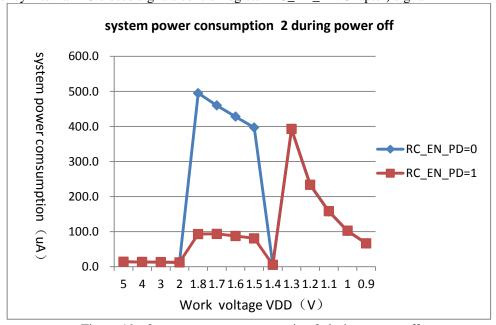

| 19.7 | SYSTEM POWER CONSUMPTION DURING POWER OFF    | 110 |

| 19.8 | OTHER ELECTRICAL CHARACTERISTICS             | 111 |

| 20 D | DEVELOPMENT TOOLS                            | 112 |

| 20.1 | EMULATOR CHARACTERISTICS                     | 112 |

| 20.2 | PROGRAMMER TOOLS                             | 112 |

| 20.3 | S SOFTWARE DOWNLOAD                          | 112 |

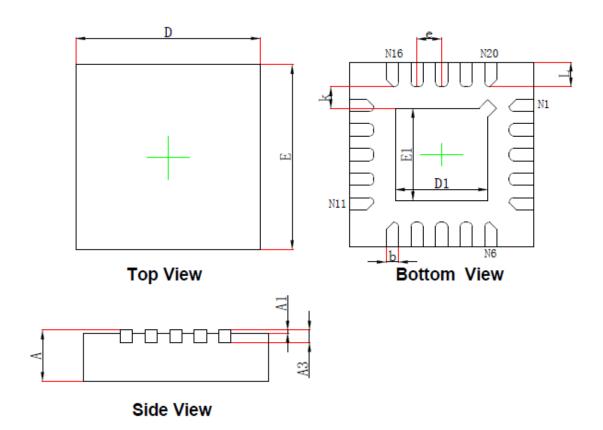

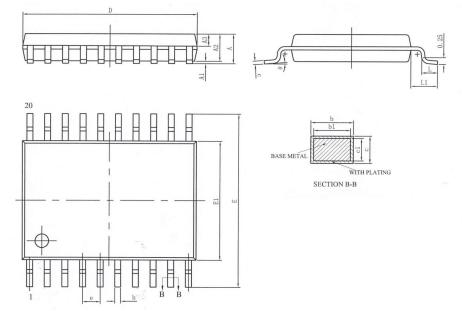

| 21 P | ACKAGE                                       | 113 |

| 21.1 | TSSOP20                                      | 113 |

| 22 R | EVERSION HISTORY                             | 114 |

# 1 Description

HC89S003F4 is an enhanced 8 bit microcontroller with high frequency and low power consumption CMOS process. 16K bytes flash program memory, 256 bytes IRAM and 256 bytes XRAM, 18 bi-directional I/O, five 16-bit Timer/counters, 3 groups 12 bits complementary PWM with dead-time control, one 8bits PWM, 2 UART, 1 SPI, 16 external interrupts, 8+2 channels 12 bits ADC, 4 system work modes (normal, low frequency, power-down, idle) and 16 interrupt sources.

#### 1.1 Features

- **♦** CPU

- Enhanced 1T 8051 core

- ◆ ROM

- 16K bytes flash

- Support IAP and ICP operation

- Flexible code protection mode

- ◆ RAM

- 256 bytes IRAM

- 256 bytes XRAM

- ◆ Clock

- Internal high precision (±1%) 32MHz RC

- Internal 44 KHz RC

- External high frequency oscillator 4MHz-24MHz

- External low frequency oscillator 32.768KHz

- Multiple clock output

- **♦** RESET

- Power on reset (POR)

- Multistep low voltage reset (BOR) 4.2/3.9/3.6/3.0/2.6/2.4/2.0/1.8V

- Watchdog Timer reset

- Software reset

- Stack overflow reset

- External pin low voltage reset

- External pin voltage (1.2V) detection reset

- **♦ I/O**

- 18 bi-directional IO

- Multiple modes configurable: input, pull-up input, pull-down input, Schmitt input, analog input, strong push pull output, open drain output, open drain output with pull-up,

- Peripheral function Ports total mapping module

- ♦ interrupt

- 16 interrupt sources

- 4 level interrupt priorities

- 16 external interrupts

- **♦** Timer/Counter

- T0/T1 compatible with standard 8051, 16-bit auto reload

- T3 can run in power-down mode

- T4 can be trigged by external signal

- T5 with capture function

- ◆ PWM

- Up to 3 groups 12 bits complementary PWM with dead-time control

- Configurable 6 channels independent output

- Can used as Timer

- Malfunction detection function

- 1 channel 8 bit PWM output

- **♦** Communication interfaces

- 2 UART

- 1 SPI

- **♦** Analog to digital converter (ADC)

- 12 bit ADC, up to 8+2 multiple channels

- ADC reference voltage: internal VREF, external VREF, and VDD

- Power saving wakeup function (single channel)

- **♦** Low voltage detection module

- Multilevel voltage detection with interrupt 4.2/3.9/3.6/3.0/2.6/2.4/2.0/1.9V

- Cyclic redundancy check(CRC)

- **♦** Power saving mode

- Idle mode

- power-down mode

- **♦** Operating conditions

- Wide operating voltage 2.0V to 5.5V

- Temperature range  $-40^{\circ}$ C to  $+85^{\circ}$ C

- **♦** Package

- TSSOP20

- SOP/TSSOP/QFN20

#### ✓ Selection table

| Device     | ROM | RAM     | I/O | Timer   | PWM           | A/D | INT | PCA | IIC | UART | SPI | WDT | Voltage | TEMP | Package |

|------------|-----|---------|-----|---------|---------------|-----|-----|-----|-----|------|-----|-----|---------|------|---------|

| HC89S003F4 | 16K | 256+256 | 18  | 16bit*5 | 12bit*3 group | 8+2 | 16  | ,   | ,   | 2    |     | 1   | 2.0~    | -40~ | TSSOP20 |

| HC895005F4 | 10K | 230+236 | 18  | 10011"3 | +8bit*1 group | 8+2 | 10  | /   | /   | 2    | 1   | 1   | 5.5V    | +85℃ | 155OP20 |

#### HC89S003F4 use attentions:

- 1. In order to ensure the system stability, user must connect a capacitor (≥0.1μF) between VDD and GND.

- 2. When user use ADC module, no matter what the reference voltage is selected, the system voltage VDD must above 2.7V.

- 3. When external interrupt in query mode, interrupt flag cannot be cleared normally. User must disable interrupt enable bit first, then clear interrupt flag, after completion of clearing the interrupt flag, then enable external interrupt to generate normal external interrupt query. No problem in interrupt mode.

- 4. When user use T3 counter clock source to select external clock of port input, TR3 and T3CLKS [1:0] should be configured simultaneously (that is to say, user should uses one instruction to complete the configuration).

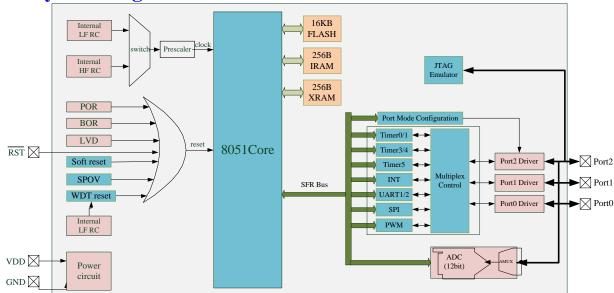

### 1.2 System diagram

Figure 1-1 System diagram

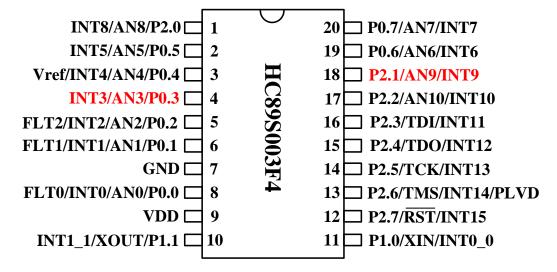

#### **TSSOP20**

Figure 1-2 TSSOP20

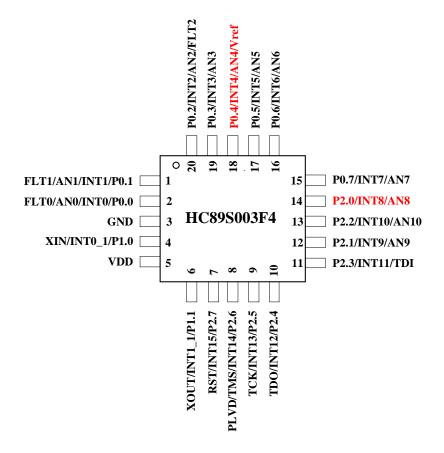

### QFN20

Figure 1-3 QFN20

### 1.3 Pin configuration

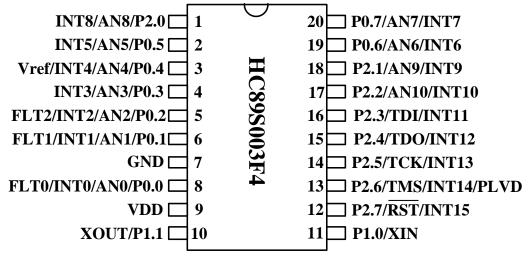

### 1.3.1 SOP20/TSSOP20 Pin configuration

Figure 1-2 SOP20/TSSOP20 pin configuration diagram

### 1.4 Pin description

| Pin | Name | Type | Introductions                                    |  |  |  |  |  |  |

|-----|------|------|--------------------------------------------------|--|--|--|--|--|--|

|     | P2.0 | I/O  | Input/output port                                |  |  |  |  |  |  |

| 1   | AN8  | AN   | ADC8 input port                                  |  |  |  |  |  |  |

|     | INT8 | I    | External interrupt 8, input port                 |  |  |  |  |  |  |

|     | P0.5 | I/O  | Input/output port                                |  |  |  |  |  |  |

| 2   | AN5  | AN   | ADC5 input port                                  |  |  |  |  |  |  |

|     | INT5 | I    | External interrupt 5, input port                 |  |  |  |  |  |  |

|     | P0.4 | I/O  | Input/output port                                |  |  |  |  |  |  |

| 3   | AN4  | AN   | ADC4 input port                                  |  |  |  |  |  |  |

| 3   | Vref | AN   | ADC external reference voltage input/output port |  |  |  |  |  |  |

|     | INT4 | I    | External interrupt 4, input port                 |  |  |  |  |  |  |

|     | P0.3 | I/O  | Input/output port                                |  |  |  |  |  |  |

| 4   | AN3  | AN   | ADC3 input port                                  |  |  |  |  |  |  |

|     | INT3 |      | External interrupt 3, input port                 |  |  |  |  |  |  |

|     | P0.2 | I/O  | Input/output port                                |  |  |  |  |  |  |

| 5   | AN2  | I    | ADC2 input port                                  |  |  |  |  |  |  |

| 3   | INT2 | I    | External interrupt 2, input port                 |  |  |  |  |  |  |

|     | FLT2 | 1    | PWM2 fault detection of input pins               |  |  |  |  |  |  |

|     | P0.1 | I/O  | Input/output port                                |  |  |  |  |  |  |

| 6   | AN1  | I    | ADC1 input port                                  |  |  |  |  |  |  |

| U   | INT1 | Ī    | External interrupt 1, input port                 |  |  |  |  |  |  |

|     | FLT1 |      | PWM1 fault detection of input pins               |  |  |  |  |  |  |

| 7   | GND  | P    | Power ground                                     |  |  |  |  |  |  |

|     | P0.0 | I/O  | Input/output port                                |  |  |  |  |  |  |

| 8   | AN0  | AN   | ADC0 input port                                  |  |  |  |  |  |  |

| O   | INT0 | I    | External interrupt 0, input port                 |  |  |  |  |  |  |

|     | FLT0 | I    | PWM0 fault detection of input pins               |  |  |  |  |  |  |

| 9   | VDD  | P    | Power input                                      |  |  |  |  |  |  |

| 10  | P1.1 | I/O  | Input/output port                                |  |  |  |  |  |  |

| 10  | XOUT | 1/0  | External oscillator output                       |  |  |  |  |  |  |

| 11  | P1.0 | I/O  | Input/output port                                |  |  |  |  |  |  |

| 11  | XIN  | 1/0  | External oscillator input                        |  |  |  |  |  |  |

| 12  | P2.7 | I/O  | Input/output port                                |  |  |  |  |  |  |

|     | RST    | I   | External reset input port         |  |  |  |  |  |

|-----|--------|-----|-----------------------------------|--|--|--|--|--|

|     | INT15  | I   | External interrupt 15, input port |  |  |  |  |  |

|     | P2.6   | I/O | Input/output port                 |  |  |  |  |  |

| 1.2 | TMS    | I   | JTAG mode input                   |  |  |  |  |  |

| 13  | INT14  | I   | External interrupt 14, input port |  |  |  |  |  |

|     | PLVD   | AN  | Port low voltage detection port   |  |  |  |  |  |

|     | P2.5   | I/O | Input/output port                 |  |  |  |  |  |

| 14  | TCK    | I   | JTAG clock input                  |  |  |  |  |  |

|     | INT13  | I   | External interrupt 13, input port |  |  |  |  |  |

|     | P2.4   | I/O | Input/output port                 |  |  |  |  |  |

| 15  | TDO    | O   | JTAG data output                  |  |  |  |  |  |

|     | INT12  | I   | External interrupt 12, input port |  |  |  |  |  |

|     | P2.3 I |     | Input/output port                 |  |  |  |  |  |

| 16  | TDI    | I   | JTAG data input                   |  |  |  |  |  |

|     | INT11  | I   | External interrupt 11, input port |  |  |  |  |  |

|     | P2.2   | I/O | Input/output port                 |  |  |  |  |  |

| 17  | AN10   | I   | ADC10 input port                  |  |  |  |  |  |

|     | INT10  | 1   | External interrupt 10, input port |  |  |  |  |  |

|     | P2.1   | I/O | Input/output port                 |  |  |  |  |  |

| 18  | AN9    | AN  | ADC9 input port                   |  |  |  |  |  |

|     | INT9   | I   | External interrupt 9, input port  |  |  |  |  |  |

|     | P0.6   | I/O | Input/output port                 |  |  |  |  |  |

| 19  | AN6    | AN  | ADC6 input port                   |  |  |  |  |  |

|     | INT6   | I   | External interrupt 6, input port  |  |  |  |  |  |

|     | P0.7   | I/O | Input/output port                 |  |  |  |  |  |

| 20  | AN7    | AN  | ADC7 input port                   |  |  |  |  |  |

|     | INT7   | I   | External interrupt 7, input port  |  |  |  |  |  |

### 1.5 Peripheral function Ports total mapping module PTM

HC89S003F4 has peripheral function Ports total mapping module internal, by software user can configure most peripheral function to arbitrary port except power port (VDD, GND).

#### 1.5.1 PTM module characteristics

- When set peripheral port as input (T0/1/3/5 external input, RXD and so on) function, system permit multi to one mapping, that is multi-input peripheral functions port are distributed the same IO, the method will optimize the user's system.

- When set peripheral port as output (T0/1/4 clock output, TXD and so on) function, if multi-output peripheral functions port are distributed the same IO, it will follow fixed priority, only one output is valid.

- Software operation, use flexible, when use design system, don't care the Pins layout of peripheral functions, it can reduce the development cost.

- When user meets layout errors of peripheral function Pins on PCB, user can re-distribute peripheral functions by PTM module, and shorten development period.

- When user changes the peripheral components during system design, only need minimum changes, it will reduce the cost of system maintenance.

1.5.2 PTM support peripheral function Ports total mapping

|            | The state of the s | P    | protection 1 of 65 total mapping          |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------|

| Peripheral | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Type | Instructions                              |

| T.         | Т0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I/O  | T0 external input orT0 clock scale output |

|            | T1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I/O  | T1 external input orT1 clock scale output |

| Timer      | T3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I    | T3 external input                         |

|            | T4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | О    | T4 ouput                                  |

|         | T5     | I   | T5 external input                            |  |  |  |

|---------|--------|-----|----------------------------------------------|--|--|--|

|         | PWM0 O |     | PWM0 output port                             |  |  |  |

| PWM01 O |        | О   | PWM01 output port                            |  |  |  |

|         | PWM1   | О   | PWM1 output port                             |  |  |  |

| PWM     | PWM11  | О   | PWM11 output port                            |  |  |  |

|         | PWM2   | О   | PWM2 output port                             |  |  |  |

|         | PWM21  | О   | PWM21 output port                            |  |  |  |

|         | PWM3   | О   | PWM3 output port                             |  |  |  |

| CLK     | CLKO   | О   | Clock output port                            |  |  |  |

|         | TXD    | О   | UART1 data transmission port                 |  |  |  |

| UART    | RXD    | I/O | UART1 receive port                           |  |  |  |

| UAKI    | TXD2   | О   | UART2 data transmission port                 |  |  |  |

| RXD2 I  |        | I   | UART2 receive port                           |  |  |  |

|         | MOSI   | I/O | SPI data port, master output and slave input |  |  |  |

| SPI     | MISO   | I/O | SPI data port, master input and slave output |  |  |  |

| SFI     | SCK    | I/O | SPI clock port                               |  |  |  |

|         | SS     | I   | SPI chip select port                         |  |  |  |

**1.5.3 PTM dose not support peripheral function Ports total mapping** PTM does not support peripheral function Ports total mapping include power port(VDD, GND),PWM fault detection Pin (FLT0/1/2), ADC input, INT0-15 function port, oscillator Pin(Xin,XOUT), external reset Port(RST), LVD voltage detection port(LVDI).

### 2 CPU

### 2.1 CPU characteristics

HC89S003F4 CPU is an enhanced 1T compatible with 8051 core, it run faster than traditional 8051 under the same system clock, and has better performance characteristics.

### 2.2 CPU registers

### 2.2.1 PC program counter PC

Program counter PC is independent physically, does not belong to SFR. PC word length is 16 bits, and used to control the execution sequence of instructions register. After microcontroller power on or reset, PC value is 0000H, program is executed from 0000H address, if second reset vector is enabled, then after power on or reset, microcontroller will execute program from the second reset vector address.

#### 2.2.2 Accumulator ACC

Accumulator (ACC) as A in instruction system, and used to provide ALU operands and store the arithmetic result, it is CPU most frequent work register, most execution of the instructions via the accumulator ACC.

### 2.2.3 Register B

Register  $\bar{B}$  is set for multiplication and division registers specifically, used to store the operands and result of the arithmetic of multiplication and division. at the time no multiplication or division, it can be used as a general purpose register.

### 2.2.4 Program state word register PSW

This register is used to save characteristics and the processing state of the ALU arithmetic result, and the characteristics and state as the condition of controlling program transfer, for program checking and querying, the bits are defined as follows:

| Bit          | 7   | 6   | 5   | 4   | 3    | 2   | 1   | 0 |

|--------------|-----|-----|-----|-----|------|-----|-----|---|

| R/W          | R/W | R/W | R/W | R/W | R/W  | R/W | R/W | R |

| Reset values | 0   | 0   | 0   | 0   | 0    | 0   | 0   | 0 |

| Flag         | CY  | AC  | F0  | RS[ | 1:0] | OV  | F1  | P |

| Bit | Flag    | Introductions                                             |  |  |  |  |  |  |

|-----|---------|-----------------------------------------------------------|--|--|--|--|--|--|

| 7   | CY      | Carry/borrow flag 0 : In arithmetic, no a carry or borrow |  |  |  |  |  |  |

|     |         | 1 : In arithmetic, carry or borrow has occurred           |  |  |  |  |  |  |

|     |         | Auxiliary carry/borrow flag                               |  |  |  |  |  |  |

| 6   | AC      | 0 : In arithmetic, no auxiliary carry or borrow           |  |  |  |  |  |  |

|     |         | 1 : In arithmetic, auxiliary carry or borrow has occurred |  |  |  |  |  |  |

| 5   | F0      | User-defined flag                                         |  |  |  |  |  |  |

|     |         | register group selection flag                             |  |  |  |  |  |  |

|     |         | 00 : 0 Group ( 00H ~ 07H )                                |  |  |  |  |  |  |

| 4-3 | RS[1:0] | 01 : 1 Group ( 08H ~ 0FH )                                |  |  |  |  |  |  |

|     |         | 10 : 2 Group ( 10H ~ 17H )                                |  |  |  |  |  |  |

|     |         | 11 : 3 Group ( 18H ~ 1FH )                                |  |  |  |  |  |  |

|     |         | Overflow flag                                             |  |  |  |  |  |  |

| 2   | OV      | 0: no overflow                                            |  |  |  |  |  |  |

|     |         | 1 : Overflow has occurred                                 |  |  |  |  |  |  |

| 1   | F1      | User-defined flag                                         |  |  |  |  |  |  |

|     |         | Parity bit                                                |  |  |  |  |  |  |

| 0   | P       | 0 : sum of 1 in ACC register is 0 or even                 |  |  |  |  |  |  |

|     |         | 1 : Sum of 1 in ACC register is odd                       |  |  |  |  |  |  |

### 2.2.5 Stack pointer SP

SP is a 8 bits special register, it indicates the top of the stack in the internal RAM position. After MCU reset,SP value is 07H, the stack was actually performed from the 08H unit, considering the 08H~1FH units belong to work register 1~3 respectively, and if in the program user needs to use these areas, the SP value better should be set a large value. 51MCU stack is upward generated, such as: SP=30H,after CPU execute a instruction or response a interrupt,PC push stack, PCL protected to 31H,PCH protected to 32H,SP=32H.

#### 2.2.6 Data pointer DPTR

Data pointer DPTR is a 16 bits special register, it is consists of two 8 registers DPH (high 8 bits) and DPL (low 8 Bits). The series MCU has two 16 bits data pointer of DPTR0 and DPTR1, they share the same address, user can set DPS (INSCON. 0) to select the data pointer.

### 2.2.7 Data pointer select register INSCON

| Bit          | 7 | 6 | 5 | 4    | 3 | 2 | 1 | 0   |

|--------------|---|---|---|------|---|---|---|-----|

| R/W          | R | R | R | R/W  | R | R | R | R/W |

| Reset values | 0 | 0 | 0 | 0    | 0 | 0 | 0 | 0   |

| Flag         |   | - |   | IAPS |   | - |   | DPS |

| Bit | Flag | Introductions                                                                                      |  |  |  |  |  |  |

|-----|------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7-5 | -    | Reserved (read = 0b, write invalid)                                                                |  |  |  |  |  |  |

| 4   | IAPS | MOVC operation selection bit 0 : program area read/erase/write operation 1 : OPTION read operation |  |  |  |  |  |  |

| 3-1 | -    | Keep (read = 0b, write invalid)                                                                    |  |  |  |  |  |  |

| 0   | DPS  | Data pointer selection bit  0: Data pointer DPTR0  1: Data pointer DPTR1                           |  |  |  |  |  |  |

# 3 Memory

### 3.1 The program memory(flash)

#### 3.1.1 Flash characteristics

- Support erase and program in all operating voltage

- ➤ In-circuit programming (ICP) support write, read, and erase operations

- ➤ ICP mode supports 32 bits password protection

- In-application programming (IAP) supports user-defined startup code and flash simulation of EEPROM

- > Flexible code protection mode

- > 100k erase times at least

- > 10 years data retention at least

#### 3.1.2 Flash data security

Flash operation is divided into two modes: first mode is flash read/erase/write through flash programmer, this is called in-circuit programming mode ( ICP ), JTAG is one of ICP; second mode is the user code run in flash code area, it can read/write/erase the other sectors of flash memory, but unable to erase the code in sector itself, which is called in-application programming mode ( IAP ).

#### 3.1.2.1 User ID password protection

User can protect the ICP operation by setting password during PC software, password lengths are 4 bytes (32 bits), once password is set, only input the correct password, user can enter JTAG mode, otherwise any operation of flash is invalid, the password can protect the user's code availably.

#### 3.1.2.2 ICP read/erase/write flash protection

ICP read protection unit is 4K bytes, when 4K bytes space read protection enabled, read data is all 0 by ICP read, but user can still do simulation by ICP operation.

ICP erase and write protection unit are 4K bytes too, when the corresponding 4K bytes erase and write protection enabled, ICP will not be able to erase and program 4K bytes, strong writing is disabled.

If the corresponding 4K bytes read protection is enabled, but erase and write operations are enabled, user can get read access after erase until reset or power-down.

ICP read, erase and write protections are configured by PC software, and the detail descriptions please see HC-51LINK user manual.

#### 3.1.2.3 IAP read/erase/write flash protection

IAP read flash by the instruction MOVC, IAP read protection unit is 4K bytes, if the 4K bytes space read protection is enabled, MOVC instruction in other 4K bytes space only read out data 0 from this 4K bytes, but MOVC instruction in this 4K bytes can read the data itself.

IAP erase and write flash steps are described in flash IAP operation, IAP erase and write protection unit is 4K bytes, before IAP erase and write, the corresponding sectors erase and write protection must be disabled.

If the corresponding 4K bytes read protection is enabled, but erase and write operations are enabled, user can to get read access after erase until reset or power-down.

IAP read, erase and write protections are configured by PC software, and the detail descriptions please see HC-51LINK user manual.

#### 3.1.3 OPTION

There is a read-only OPTION area besides 16K bytes ROM, storage data include: user setting data, user passwords, chip configurations data, the second reset vector data related. Address distribution in below table.

| Address | Name     | Address<br>offset | Name      | Address | Name     | Address<br>offset | Name     |

|---------|----------|-------------------|-----------|---------|----------|-------------------|----------|

| 0x0000  | SN_DATA0 | 0x0020            | FLASH_SC0 | 0x0031  | ERST_ENB | 0x0100            | CHIP_ID0 |

| 0x0001  | SN_DATA1 | 0x0021            | FLASH_SC1 | 0x0038  | WAIT_TS  | 0x0101            | CHIP_ID1 |

| 0x0002  | SN_DATA2 | 0x0022            | FLASH_SC2 | 0x0039  | BORVS    | 0x0102            | CHIP_ID2 |

| 0x0003  | SN_DATA3 | 0x0023            | FLASH_SC3 | 0x003E  | RVCFG    | 0x0103            | CHIP_ID3 |

| 0x0004  | SN_DATA4 | -                 | -         | 0x003F  | nRVCFG   | 0x0104            | CHIP_ID4 |

| 0x0005  | SN_DATA5 | -                 | -         | -       | -        | 0x0105            | CHIP_ID5 |

| 0x0006  | SN_DATA6 | -                 | -         | -       | -        | 0x0106            | CHIP_ID6 |

| 0x0007  | SN_DATA7 | -                 | -         | -       | -        | 0x0107            | CHIP_ID7 |

| 0x0008  | ID_DATA0 | -                 | -         | -       | -        | -                 | -        |

| 0x0009  | ID_DATA1 | -                 | -         | -       | -        | -                 | -        |

| 0x000A  | ID_DATA2 | -                 | -         | -       | -        | -                 | -        |

| 0x000B  | ID_DATA3 | -                 | -         | -       | -        | -                 | -        |

| 0x000C  | ID_DATA4 | -                 | -         | -       | -        | -                 | -        |

| 0x000D  | ID_DATA5 | -                 | -         | -       | -        | -                 | -        |

| 0x000E  | ID_DATA6 | -                 | -         | -       | -        | -                 | -        |

| 0x000F  | ID_DATA7 | -                 | -         | -       | -        | -                 | -        |

HC89S003F4 will be configured a 8 bytes CHIP\_ID before leave the factory, the CHIP\_ID is unique and not repeated, user can read it by MOVC instruction in code.

SN\_DATA and ID\_DATA are user-defined data, FLASH\_SC is user password, it is set by software tools, as well as setting code options, they can be erased or modified, and user can read them by MOVC instruction in code.

Note: 1. User must set register INSCON[IAPS] bit to 1 before read OPTION.

2. First character "n" is complement of the corresponding data.

#### 3.1.3.1 External reset enabled (ERST ENB)

|      |     |  |       | · / |   |     |  |          |

|------|-----|--|-------|-----|---|-----|--|----------|

| Bit  | 7 6 |  | 6 5 4 |     | 3 | 3 2 |  | 0        |

| Flag |     |  |       | -   |   |     |  | ERST_ENB |

| Bit | Flag     | Introductions                                              |

|-----|----------|------------------------------------------------------------|

| 7-1 | -        | Reserved bits                                              |

| 0   | ERST_ENB | Reset pin enable bit 0: External RST input 1: P2.7 as GPIO |

#### 3.1.3.2 Wait time of reread OPTION after reset (WAIT\_TS)

| Bit  | 7 | 6 | 5 | 4 | 3 | 2 | 1       | 0 |

|------|---|---|---|---|---|---|---------|---|

| Flag | - | - | - | - | - | - | WAIT_TS |   |

| Bit | Flag    | Introductions                                                               |

|-----|---------|-----------------------------------------------------------------------------|

| 7-2 | -       | Reserved bits                                                               |

| 1-0 | WAIT_TS | Wait time of reread option after reset selection bits 00:8ms 01:4ms 11:16ms |

### 3.1.3.3 BOR detection voltage selection (BORVS)

| Bit  | 7 | 6 | 5 | 4 | 3 | 2     | 1 | 0 |

|------|---|---|---|---|---|-------|---|---|

| Flag | - | - | - | - | - | BORVS |   |   |

| Bit | Flag  | Introductions                                                                                                                                   |

|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-3 | -     | Reserved bits                                                                                                                                   |

| 2-0 | BORVS | BOR detection of voltage selection bits<br>000: 1.8V<br>001: 2.0V<br>010: 2.4V<br>011: 2.6V<br>100: 3.0V<br>101: 3.6V<br>110: 3.9V<br>111: 4.2V |

#### 3.1.3.4 Second reset vector configuration (RVCFG)

|      |       |   | <del> </del> | ( ) |   |      |         |   |

|------|-------|---|--------------|-----|---|------|---------|---|

| Bit  | 7     | 6 | 5            | 4   | 3 | 2    | 1       | 0 |

| Flag | RVSEN |   | -            |     |   | RVAD | PR[3:0] | • |

| Bit | Flag       | Introductions                                                           |

|-----|------------|-------------------------------------------------------------------------|

| _   |            | The second reset vector enable bit                                      |

| 7   | RVSEN      | 0: disable the second reset vector                                      |

|     |            | 1: enable the second reset vector                                       |

| 6-4 | -          | Reserved bits                                                           |

|     |            | The second reset vector configuration values                            |

|     |            | The second reset vector address = {RVADR[3:0],00000000000B}             |

|     |            | Note:                                                                   |

| 3-0 | RVADR[3:0] | 1. When RVADR[3:0]=0, the second reset vector address coincide with     |

|     |            | 0x0000H.                                                                |

|     |            | 2. RVADR[3:0] configuration data only equal 1000, 1100, 1110, 1111 four |

|     |            | values, the second reset vector space only is 1K, 2K, 4K, 8K.           |

### 3.1.4 Flash IAP operation

Before flash IAP erase and write, user need to configure extension SFR FREQ\_CLK register, and indicates the current CPU frequency, FREQ\_CLK configuration value is equal to CPU clock frequency, the minimum value is 1MHz, If CPU current frequency is 16MHz, user must configure the value in register FREQ\_CLK=0x10 . Recommended before IAP erase and write, CPU clock frequency division factor is an integer. When CPU clock frequency below 1MHz, flash IAP erase and write operation is disabled.

#### 3.1.4.1 IAP data register (IAP\_DATA)

| Bit             | 7   | 6             | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-----------------|-----|---------------|-----|-----|-----|-----|-----|-----|--|--|

| R/W             | R/W | R/W           | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Reset<br>values | 0   | 0             | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

|                 |     |               |     |     |     |     |     |     |  |  |

| Flag            |     | IAP_DATA[7:0] |     |     |     |     |     |     |  |  |

| I | Bit | Flag          | Introductions     |

|---|-----|---------------|-------------------|

|   | 7-0 | IAP_DATA[7:0] | IAP data register |

# 3.1.4.2 IAP address register IAP\_ADDRL, IAP\_ADDRH IAP\_ADDRL

| Bit    | 7   | 6             | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|--------|-----|---------------|-----|-----|-----|-----|-----|-----|--|--|

| R/W    | R/W | R/W           | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Reset  | 1   | 1             | 1   | 1   | 1   | 1   | 1   | 1   |  |  |

| values | 1   | 1             | 1   | 1   | 1   | 1   | 1   | 1   |  |  |

| Flag   |     | IAP_ADDR[7:0] |     |     |     |     |     |     |  |  |

| Bit | Flag          | Introductions                                    |

|-----|---------------|--------------------------------------------------|

| 7-0 | IAP_ADDR[7:0] | Low 8 bits of the IAP operation address register |

#### IAP\_ADDRH

| Bit          | 7 | 6 | 5   | 4   | 3              | 2   | 1   | 0   |  |

|--------------|---|---|-----|-----|----------------|-----|-----|-----|--|

| R/W          | R | R | R/W | R/W | R/W            | R/W | R/W | R/W |  |

| Reset values | 0 | 0 | 1   | 1   | 1              | 1   | 1   | 1   |  |

| Flag         | - |   |     |     | IAP_ADDR[13:8] |     |     |     |  |

| Bit | Flag           | Introductions                                     |

|-----|----------------|---------------------------------------------------|

| 7-6 | -              | Reserved                                          |

| 5-0 | IAP_ADDR[13:8] | High 6 bits of the IAP operation address register |

Note: User can modify IAP address register only in unlocked status, and once operation is completed, IAP address is pointed to 0x3FFF automatically.

# 3.1.4.3 IAP Command register IAP\_CMDH, IAP\_CMDL IAP\_CMDH

| Bit          | 7             | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------------|---------------|-----|-----|-----|-----|-----|-----|-----|

| R/W          | R/W           | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset values | 0             | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Flag         | IAP_CMDH[7:0] |     |     |     |     |     |     |     |

| Bit | Flag          | Introductions                                                                                                                                                                                                                                                                                                                        |

|-----|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0 | IAP_CMDH[7:0] | Operation mode selection bit  0xF0: Unlock (22 CPU clock automatically locked, IAP_CMD[7:0] = 0x00)  0xE1: Trigger one time action  0xD2: Sector erase  0xB4: Byte program  0x87: Software reset, reset address 0000H, not reread codes options  0x78: Software reset, reset address 0000H, reread codes options  Other values: lock |

#### IAP CMDI

| Bit          | 7   | 6             | 5   | 4   | 3   | 2   | 1   | 0   |

|--------------|-----|---------------|-----|-----|-----|-----|-----|-----|

| R/W          | R/W | R/W           | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset values | 1   | 1             | 1   | 1   | 1   | 1   | 1   | 1   |

| Flag         |     | IAP_CMDL[7:0] |     |     |     |     |     |     |

| Bit | Flag          | Introductions                                                                                                                                                                                   |

|-----|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0 | IAP_CMDL[7:0] | IAP_CMDH[7:0] complement code Note: Write into IAP_CMDL[7:0] data must equal the complement of IAP_CMDH[7:0] data previous, otherwise operations will be locked, meanwhile operation will fail. |

#### Examples:

```

1, Program space sector erase

IAP CMDH = 0xF0;

IAP CMDL = 0x0F;

IAP ADDRL = 0x80;

IAP ADDRH = 0x00;

// Select first sector to be erased, a sector for 128 bytes

// Select operation mode, sector erase

IAP\_CMDH = 0xD2;

IAP\_CMDL = 0x2D;

IAP\_CMDH = 0xE1;

// Trigger

IAP\_CMDL = 0x1E;

// After trigger IAP_ADDRL Links to 0xFF, IAP_ADDRH Links to 0x3F,

meanwhile locked automatically

2, program space byte program

IAP DATA = 0x02; //Data ready to be programmed before writing data register must be unlocked

IAP CMDH = 0xF0;

IAP CMDL = 0x0F;

IAP ADDRH = 0x00;

```

IAP\_ADDRH = 0x00; IAP\_ADDRL = 0x00; IAP\_CMDH = 0xB4; // Select the mode of operation, byte program IAP\_CMDL = 0x4B; IAP\_CMDH = 0xE1; // Trigger

IAP\_CMDL = 0x1E; // After the trigger IAP\_ADDRL Links to 0xFF, IAP\_ADDRH Links to 0x3F, IAP\_DATA Links to 0x00, meanwhile locked automatically

Note: After unlocked, write address, select operation mode, trigger, between these three steps, any instruction cannot be inserted, and must be operated continuously.

3, Software reset (do not reread code options)

$IAP\_CMDH = 0xF0;$   $IAP\_CMDL = 0x0F;$   $IAP\_CMDH = 0x87;$  $IAP\_CMDL = 0x78;$

4, Software reset ( reread code options)

$IAP\_CMDH = 0xF0;$   $IAP\_CMDL = 0x0F;$   $IAP\_CMDH = 0x78;$  $IAP\_CMDL = 0x87;$

### 3.1.5 Flash ICP operation

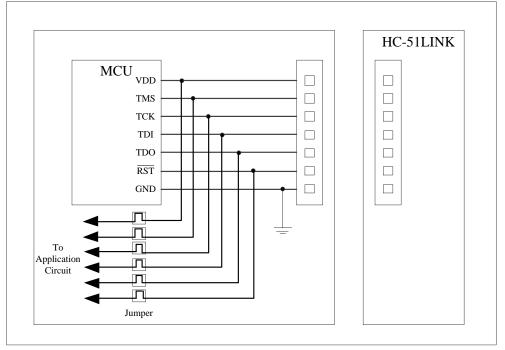

User can use HC-51LINK emulator to program MCU, after MCU is already welded in the user board, if user uses power-on reset enter JTAG mode, only links 6 cables, and user must power-down the system, and power supplied by the emulator. When user does not want to power-down the system, it need 7 cables to enter the programming mode, add a reset Pin, detailed instructions of emulator, please see HC-51LINK user manual.

In addition, because the programming signals are very sensitive, user needs to use 6 jumpers to separate programming Pins (VDD, TDO, TDI, TMS, TCK,  $\overline{RST}$ ) from the circuit, as shown in below figure.

Figure 3 - 1 HC-51LINK programming hardware connection

When using ICP operation mode, it is recommended operation according to the following steps:

- 1, Disconnect jumpers ( jumper) before start programming, , separate programming pins from the application circuit.

- 2, Connect the chip programming Pin flash program interface, then start programming.

- 3, After the program ends, disconnect flash Programming interfaces, connect jumper to application circuit.

Note: Chip power on, reset Pin is valid in default, and low level is reset, so when user use the reset Pin , it cannot be set pull-down, otherwise the chip is in the reset state always, and cannot be programming and simulation.

#### 3.1.6 Second reset vector operations

If the user has configured second reset vector enabled in the code options and the second reset vector address, then after the on-chip power-on reset, PC first point to the second vector address, and begin to implement user's startup program, if at the end of user code need place a un-reread code item of software reset program, that user program will be reset to 0x0000H, start to implement the user application program.

### 3.2 Data storage (RAM)

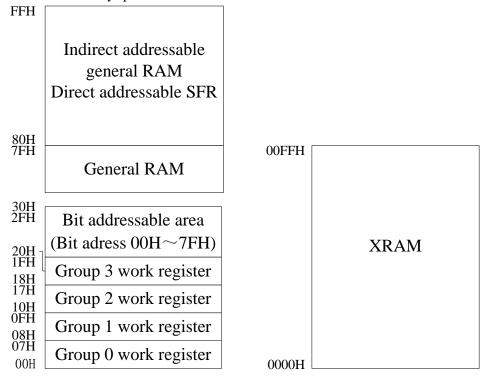

HC89S003F4 provide user with a 256 bytes internal RAM and 256 bytes internal expansion RAM as data memory. Below is data memory space allocation.

Figure 3 - 2 Data memory map

Internal RAM high 128 bytes (0x80 ~ 0xFF) must use the register indirect addressing modes. Internal expansion RAM ( XRAM ) addresses range is 0x0000 ~ 0x00FF, and access to internal extensions RAM methods same as traditional 8051 access external extensions RAM, but it does not affect I/O port. In assembly language, access internal expansion RAM through MOVX instruction, as MOVX @DPTP or MOVX @Ri.

### 3.3 Special function registers (SFR)

### 3.3.1 Special function registers list

3.3.1.1 Direct addressing, read and write SFR

|    | 0/8   | 1/9       | 2/A       | 3/B      | 4/C      | 5/D      | 6/E     | 7/F     |

|----|-------|-----------|-----------|----------|----------|----------|---------|---------|

| F8 | RSTFR | IAP_ADDRL | IAP_ADDRH | IAP_DATA | IAP_CMDL | IAP_CMDH | -       | -       |

| F0 | В     | PWM2EN    | PWM2PL    | PWM2PH   | PWM2DL   | PWM2DH   | PWM2DTL | PWM2DTH |

| E8 | -     | PWM1EN    | PWM1PL    | PWM1PH   | PWM1DL   | PWM1DH   | PWM1DTL | PWM1DTH |

| E0 | ACC   | PWM0EN    | PWM0PL    | PWM0PH   | PWM0DL   | PWM0DH   | PWM0DTL | PWM0DTH |

| D8 | -     | -         | PWM0C     | PWM1C    | PWM2C    | PWM3C    | PWM3P   | PWM3D   |

| D0 | PSW   | -         | -         | -        | -        | -        | -       | -       |

| C8 | -     | T3CON     | TL3       | TH3      | T4CON    | TL4      | TH4     | -       |

| C0 | -     | T5CON     | TL5       | TH5      | RCAP5L   | RCAP5H   | -       | -       |

| В8 | IE1   | IP2       | IP3       | LVDC     | -        | WDTC     | CRCL    | CRCH    |

| В0 | -     | -         | 1         | -        | ADCC0    | ADCC1    | ADCRL   | ADCRH   |

| A8 | ΙE    | IP0       | IP1       | SPDAT    | SPCTL    | SPSTAT   | -       | -       |

| A0 | P2    | -         | INSCON    | 1        | -        | 1        | 1       | -       |

| 98 | SCON  | SBUF      | SADDR     | SADEN    | -        | -        | SCON2   | -       |

| 90 | P1    | -         | -         | -        | -        | -        | PINTF0  | PINTF1  |

| 88 | TCON  | TMOD      | TL0       | TL1      | TH0      | TH1      | CLKSWR  | CLKCON  |

| 80 | P0    | SP        | DPL       | DPH      | -        | -        | -       | PCON    |

#### 3.3.1.2 External extension XSFR

The method to access extension XSFR is the same as XRAM, use MOVX A, @DPTR and MOVX @DPTR,A to read and write.

For example: write XSFR at address 0xFE88, operation as below:

MOV A, #wdata MOV DPTR, #0xFE88 MOVX @DPTR, A

Read XSFR at address 0xFE89, operation as below:

MOV DPTR, #0xFE89 MOVX A, @DPTR

Extension XSFR (base address is 0xFE80)

| Lizetti Sioii 21 | DI'IL (Dasc a | dui Coo io OA  | I LOU)     |                |        |                |            |

|------------------|---------------|----------------|------------|----------------|--------|----------------|------------|

| Offset address   | XSFR          | Offset address | XSFR       | Offset address | XSFR   | Offset address | XSFR       |

| 0x0000           | TCON1         | 0x0010         | -          | 0x0020         | WDTCCR | 0x0030         | PITS0      |

| 0x0001           | -             | 0x0011         | CLKDIV     | 0x0021         | -      | 0x0031         | PITS1      |

| 0x0002           | -             | 0x0012         | FREQ_CLK   | 0x0022         | CRCC   | 0x0032         | PITS2      |

| 0x0003           | -             | 0x0013         | CLKOUT     | 0x0023         | -      | 0x0033         | PITS3      |

| 0x0004           | -             | 0x0014         | RC_PD_EN   | 0x0024         | BORC   | 0x0034         | -          |

| 0x0005           | T5CON1        | 0x0015         | SPOV_RSTEN | 0x0025         | BORDBC | 0x0035         | -          |

| 0x0006           | -             | 0x0016         | -          | 0x0026         | -      | 0x0036         | -          |

| 0x0007           | -             | 0x0017         | -          | 0x0027         | LVDDBC | 0x0037         | -          |

| 0x0008           | S2CON         | 0x0018         | ADCWC      | 0x0028         | -      | 0x0038         | PINTE0     |

| 0x0009           | S2CON2        | 0x0019         | -          | 0x0029         | -      | 0x0039         | PINTE1     |

| 0x000A           | S2BUF         | 0x001A         | -          | 0x002A         | RSTDBC | 0x003A         | -          |

| 0x000B           | -             | 0x001B         | ADCC2      | 0x002B         | -      | 0x003B         | -          |

| 0x000C           | -             | 0x001C         | -          | 0x002C         | -      | 0x003C         | INT01_PINS |

| 0x000D           | -             | 0x001D         | -          | 0x002D         | -      | 0x003D         | -          |

| 0x000E           | -             | 0x001E         | -          | 0x002E         | -      | 0x003E         | _          |

| 0x000F           | -             | 0x001F         | -          | 0x002F         | -      | 0x003F         | -          |

Extension XSFR (base address is 0xFF00)

| Offset address | XSFR  | Offset address | XSFR | Offset address | XSFR | Offset address | XSFR |

|----------------|-------|----------------|------|----------------|------|----------------|------|

| 0x0000         | P0M0  | 0x0010         | P2M0 | 0x0020         | -    | 0x0030         | -    |

| 0x0001         | P0M1  | 0x0011         | P2M1 | 0x0021         | -    | 0x0031         | -    |

| 0x0002         | P0M2  | 0x0012         | P2M2 | 0x0022         | -    | 0x0032         | -    |

| 0x0003         | P0M3  | 0x0013         | P2M3 | 0x0023         | -    | 0x0033         | -    |

| 0x0004         | -     | 0x0014         | -    | 0x0024         | -    | 0x0034         | -    |

| 0x0005         | P0LPU | 0x0015         | -    | 0x0025         | -    | 0x0035         | -    |

| 0x0006         | -     | 0x0016         | -    | 0x0026         | -    | 0x0036         | -    |

| 0x0007         | -     | 0x0017         | -    | 0x0027         | -    | 0x0037         | -    |

| 0x0008         | P1M0  | 0x0018         | -    | 0x0028         | -    | 0x0038         | -    |

| 0x0009         | -     | 0x0019         | -    | 0x0029         | -    | 0x0039         | -    |

| 0x000A         | -     | 0x001A         | -    | 0x002A         | -    | 0x003A         | -    |

| 0x000B         | -     | 0x001B         | -    | 0x002B         | -    | 0x003B         | -    |

| 0x000C         | -     | 0x001C         | -    | 0x002C         | -    | 0x003C         | -    |

| 0x000D         | -     | 0x001D         | -    | 0x002D         | -    | 0x003D         | -    |

| 0x000E         | -     | 0x001E         | -    | 0x002E         | -    | 0x003E         | -    |

| 0x000F         | -     | 0x001F         | -    | 0x002F         | -    | 0x003F         | -    |

### Extension XSFR (base address is 0xFF40)

| Offset address | XSFR   | Offset address | XSFR | Offset address | XSFR | Offset address | XSFR |

|----------------|--------|----------------|------|----------------|------|----------------|------|

| 0x0000         | P00DBC | 0x0010         | -    | 0x0020         | -    | 0x0030         | -    |

| 0x0001         | P01DBC | 0x0011         | -    | 0x0021         | -    | 0x0031         | -    |

| 0x0002         | P02DBC | 0x0012         | -    | 0x0022         | -    | 0x0032         | -    |

| 0x0003         | -      | 0x0013         | -    | 0x0023         | -    | 0x0033         | -    |

| 0x0004         | -      | 0x0014         | -    | 0x0024         | -    | 0x0034         | -    |

| 0x0005         | -      | 0x0015         | -    | 0x0025         | -    | 0x0035         | -    |

| 0x0006         | -      | 0x0016         | -    | 0x0026         | -    | 0x0036         | -    |

| 0x0007         | -      | 0x0017         | -    | 0x0027         | -    | 0x0037         | -    |

| 0x0008         | -      | 0x0018         | -    | 0x0028         | -    | 0x0038         | -    |

| 0x0009         | -      | 0x0019         | -    | 0x0029         | -    | 0x0039         | -    |

| 0x000A         | -      | 0x001A         | -    | 0x002A         | -    | 0x003A         | -    |

| 0x000B         | -      | 0x001B         | -    | 0x002B         | -    | 0x003B         | -    |

| 0x000C         | -      | 0x001C         | -    | 0x002C         | -    | 0x003C         | -    |

| 0x000D         | -      | 0x001D         | -    | 0x002D         | -    | 0x003D         | -    |

| 0x000E         | -      | 0x001E         | -    | 0x002E         | -    | 0x003E         | -    |

| 0x000F         | -      | 0x001F         | -    | 0x002F         | -    | 0x003F         | -    |

#### Extension XSFR (base address is 0xFF80)

| Offset address | XSFR     | Offset address | XSFR      | Offset address | XSFR     | Offset address | XSFR |

|----------------|----------|----------------|-----------|----------------|----------|----------------|------|

| 0x0000         | T0_MAP   | 0x0010         | PWM0_MAP  | 0x0020         | TXD_MAP  | 0x0030         | -    |

| 0x0001         | T1_MAP   | 0x0011         | PWM01_MAP | 0x0021         | RXD_MAP  | 0x0031         | -    |

| 0x0002         | -        | 0x0012         | -         | 0x0022         | -        | 0x0032         | -    |

| 0x0003         | T3_MAP   | 0x0013         | -         | 0x0023         | -        | 0x0033         | -    |

| 0x0004         | T4_MAP   | 0x0014         | PWM1_MAP  | 0x0024         | _MAP     | 0x0034         | -    |

| 0x0005         | T5_MAP   | 0x0015         | PWM11_MAP | 0x0025         | SCK_MAP  | 0x0035         | -    |

| 0x0006         | -        | 0x0016         | -         | 0x0026         | MOSI_MAP | 0x0036         | -    |

| 0x0007         | -        | 0x0017         | -         | 0x0027         | MISO_MAP | 0x0037         | -    |

| 0x0008         | -        | 0x0018         | PWM2_MAP  | 0x0028         | TXD2_MAP | 0x0038         | -    |

| 0x0009         | -        | 0x0019         | PWM21_MAP | 0x0029         | RXD2_MAP | 0x0039         | -    |

| 0x000A         | -        | 0x001A         | -         | 0x002A         | -        | 0x003A         | -    |

| 0x000B         | -        | 0x001B         | -         | 0x002B         | -        | 0x003B         | -    |

| 0x000C         | -        | 0x001C         | PWM3_MAP  | 0x002C         | -        | 0x003C         | -    |

| 0x000D         | -        | 0x001D         | -         | 0x002D         | -        | 0x003D         |      |

| 0x000E         | -        | 0x001E         | -         | 0x002E         | -        | 0x003E         | -    |

| 0x000F         | CLKO_MAP | 0x001F         | -         | 0x002F         | -        | 0x003F         | -    |

## 4 The system clock

### 4.1 Characteristics of the system clock

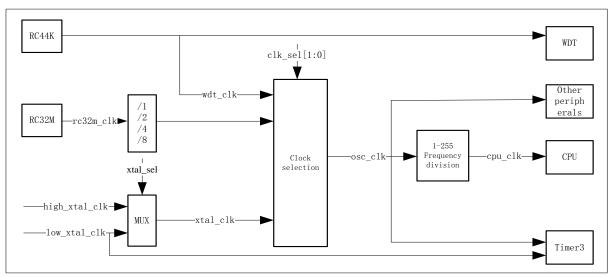

HC89S003F4 MCU system clock have 2 optional clock sources: external high-frequency RC clock (4MHz~24MHz), external low-frequency RC clock (32.768KHz), internal high-frequency RC clock (32 MHz) and internal low frequency RC clock (44KHz). The internal frequency RC scope of error is less than 1% during -40°C ~+85°C. Select the system clock (if user choose an internal high-frequency of RC, clock is divided after setting RC32M\_DIV[1:0] as osc\_clk, the frequency is  $f_{\rm OSC}$ , period is  $f_{\rm OSC}$ , mainly used for peripheral modules, osc\_clk can be divided by any value between 1-255, clock divided as CPU clock, frequency is  $f_{\rm CPU}$  period is  $f_{\rm CPU}$ .

CPU can run under 20MHz highest frequency, if frequency of clock selected is higher than 20MHz, the clock need to be divided to meet CPU Clock equal to or less than 20MHz .

Internal low frequency RC ( RC44K ) output clock marker as wdt\_clk, for the watchdog timer count, and can also be used for the system clock, internal high frequency RC ( RC32M ) output marker as rc32m\_clk, and it can be divided by 1/2/4/8. Select external oscillator marker as xtal\_clk by setting XTALCFG register.

Figure 4 - 1 System clock block diagram

### 4.2 System clock registers

### 4.2.1 Clock control register CLKCON

| Bit          | 7        | 6        | 5       | 4       | 3 | 2      | 1      | 0 |

|--------------|----------|----------|---------|---------|---|--------|--------|---|

| R/W          | R        | R        | R       | R       | R | R/W    | R/W    | R |

| Reset values | 0        | 0        | 1       | 1       | 0 | 0      | 1      | 0 |

| Flag         | HXTALRDY | LXTALRDY | HSRCRDY | LSRCRDY | - | XTALEN | HSRCEN | - |

| Bit | Flag                                                                                                                                                                                          | Introductions                                                                                                                                                                       |  |  |  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7   | HXTALRDY                                                                                                                                                                                      | External high-frequency RC oscillator state bit 0: External high-frequency RC is not ready 1: External high-frequency RC is ready Note: The hardware automatically clear 0 or set 1 |  |  |  |

| 6   | LXTALRDY  External low-frequency RC oscillator state bit  0: External low-frequency RC is not ready  1: External low-frequency RC is ready  Note: The hardware automatically clear 0 or set 1 |                                                                                                                                                                                     |  |  |  |

| 5   | HSRCRDY                                                                                                                                                                                       | Internal high-frequency RC oscillator state bit                                                                                                                                     |  |  |  |

|   |         | 0: Internal high-frequency RC is not ready 1: Internal high-frequency RC is ready Note: the hardware automatically clear 0 or set 1                                                  |

|---|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4 | LSRCRDY | Internal low frequency RC oscillator state bit 0: Internal low frequency RC is not ready 1: Internal low frequency RC is ready Note: the bit hardware automatically clear 0 or set 1 |

| 3 | -       | Reserved bit                                                                                                                                                                         |

| 2 | XTALEN  | External oscillator enable bit  0: External oscillator close 1: External oscillator open  Note: Shen enabled, need set the corresponding IO mode to analog channel by software.      |

| 1 | HSRCEN  | Internal high-frequency RC oscillator enable bit 0: Internal high-frequency RC close 1: Internal high-frequency RC open                                                              |

| 0 | -       | Reserved bit                                                                                                                                                                         |

### 4.2.2 Select clock register CLKSWR

| Bit          | 7     | 6       | 5     | 4       | 3 | 2 | 1      | 0        |

|--------------|-------|---------|-------|---------|---|---|--------|----------|

| R/W          | R     | R       | R/W   | R/W     | R | R | R/W    | R/W      |

| Reset values | 0     | 1       | 0     | 1       | 0 | 0 | 1      | 1        |

| Flag         | CLKST | ΓA[1:0] | CLKSI | EL[1:0] | - | - | RC32M_ | DIV[1:0] |

| Bit | Flag                                                                                                                                                                                                                                                                                                                                                                                                                          | Introductions                                                                                                                                                                                                                                                                                                                   |  |  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7-6 | CLKSTA[1:0]                                                                                                                                                                                                                                                                                                                                                                                                                   | System clock state bits  00: Current system clock is internal low frequency RC  01: Current system clock is internal high frequency RC  10: Current system clock is external low frequency RC  11: Current system clock is external high frequency RC  Notes: system automatically switches state based on current system clock |  |  |

| 5-4 | System clock selection bit  00: Select system clock to internal low frequency RC  01: Select system clock to internal high frequency RC  Note: corresponding clock source state bits must be set to 1 when select system clock, or use previous clock, after switching, the original clock not automatically close; select the system clock marker as osc_clk, the frequency is F <sub>osc</sub> period is T <sub>osc</sub> . |                                                                                                                                                                                                                                                                                                                                 |  |  |

| 3-2 | -                                                                                                                                                                                                                                                                                                                                                                                                                             | Reserved bit                                                                                                                                                                                                                                                                                                                    |  |  |

| 1-0 | RC32M_DIV[1:0]                                                                                                                                                                                                                                                                                                                                                                                                                | Internal high frequency RC scale bits  00 : rc32m_clk 01 : rc32m_clk /2 10 : rc32m_clk /4 11 : rc32m_clk /8(default)                                                                                                                                                                                                            |  |  |

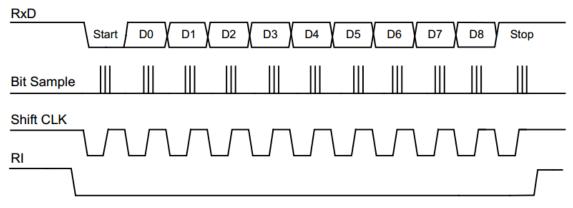

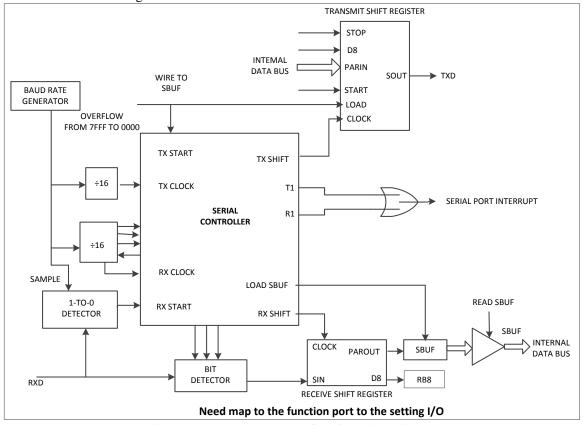

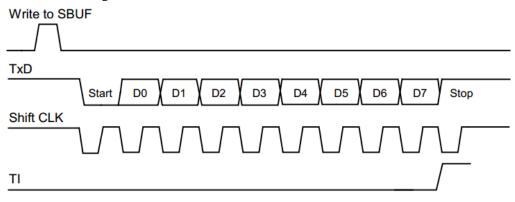

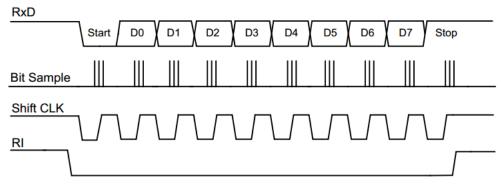

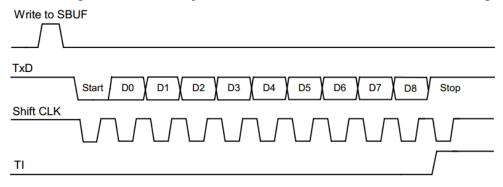

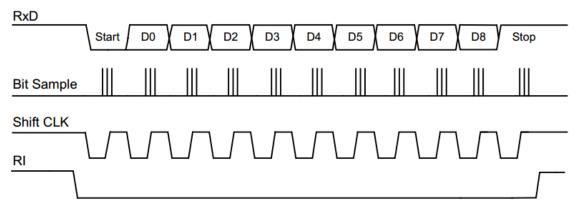

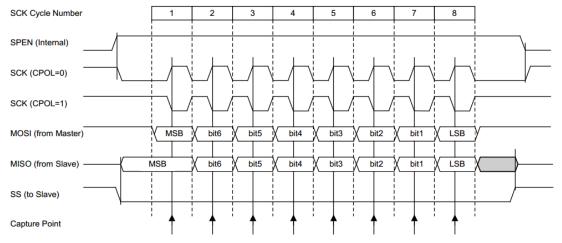

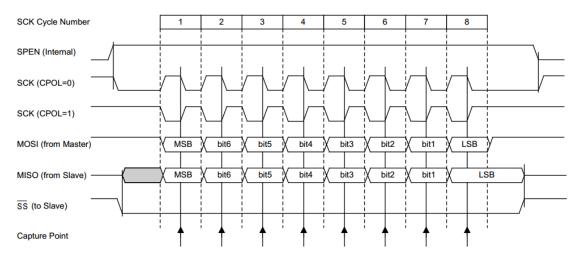

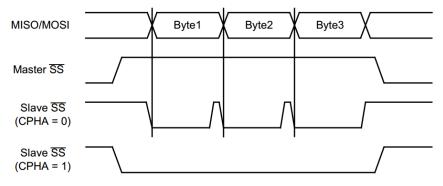

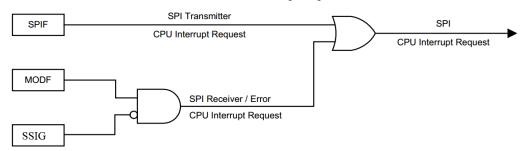

### 4.2.3 Clock scale register (CLKDIV)